MC56F826XXDS

#### MC56F826xx Supports MC56F82646VLF, MC56F82643VLC, MC56F82623VLC Features

- This family of digital signal controllers (DSCs) is based on the 32-bit 56800EX core. On a single chip, each device combines the processing power of a DSP and the functionality of an MCU, with a flexible set of peripherals to support many target applications:

- Industrial control

- Home appliances

- Motor control (ACIM, BLDC, PMSM, SR, stepper)

- DSC based on 32-bit 56800EX core

- Up to 100 MIPS at 100 MHz core frequency in fast mode

- DSP and MCU functionality in a unified, C-efficient architecture

- On-chip memory

- Up to 64 KB flash memory

- 8 KB data/program RAM

- On-chip flash memory and RAM can be mapped into both program and data memory spaces

- Analog

- Two high-speed, 5-channel, 12-bit ADCs with dynamic x1, x2, and x4 programmable amplifier

- Four analog comparators with integrated 6-bit DAC references

- One FlexPWM module with up to 6 PWM outputs

- Communication interfaces

- Up to two high-speed queued SCI (QSCI) modules with LIN slave functionality

- Timers

- One 16-bit quad timer (1 x 4 16-bit timer)

- Two Periodic Interval Timers (PITs)

- Security and integrity

- Cyclic Redundancy Check (CRC) generator

- Windowed Computer operating properly (COP) watchdog

- External Watchdog Monitor (EWM)

- Clocks

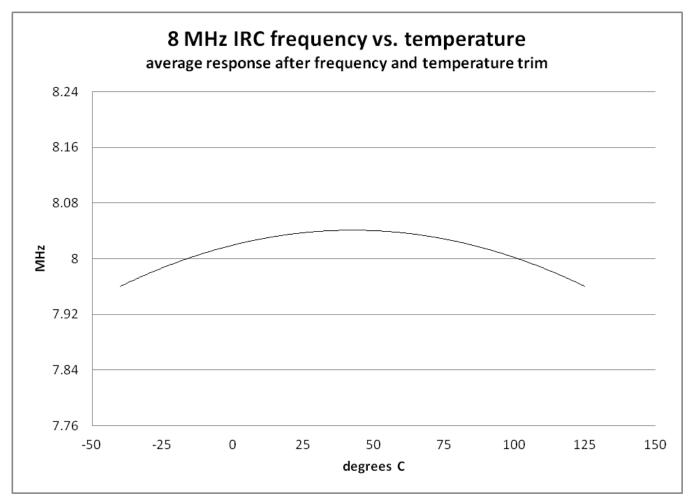

- Two on-chip relaxation oscillators: 8 MHz (400 kHz at standby mode) and 200 kHz

- Crystal / resonator oscillator

- System

- DMA controller

- Integrated power-on reset (POR) and low-voltage interrupt (LVI) and brown-out reset module

- Inter-module crossbar connection

- JTAG/enhanced on-chip emulation (EOnCE) for unobtrusive, real-time debugging

- Operating characteristics

- Single supply: 3.0 V to 3.6 V

- 5 V-tolerant I/O (except for RESETB pin which is a 3.3 V pin only)

- Operation ambient temperature: V temperature option: -40°C to 105°C

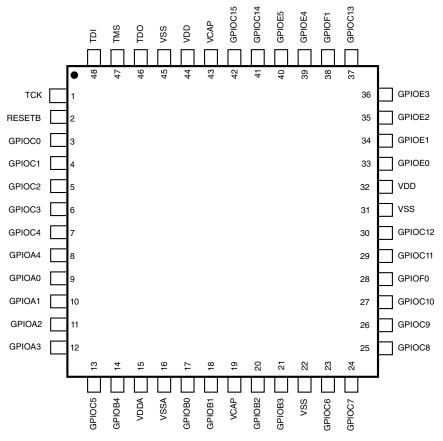

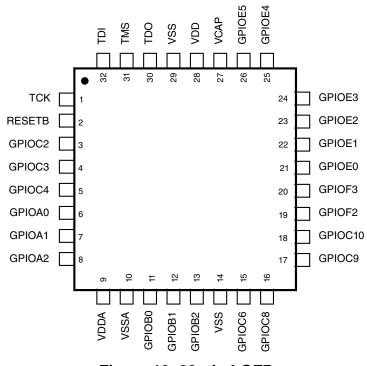

- 48-pin LQFP, and 32-pin LQFP packages

NXP reserves the right to change the production detail specifications as may be required to permit improvements in the design of its products.

# **Table of Contents**

| 1 | Over   | view                                                    | 3    |

|---|--------|---------------------------------------------------------|------|

|   | 1.1    | MC56F826xx Product Family                               | 3    |

|   | 1.2    | 56800EX 32-bit Digital Signal Controller (DSC) core     | 3    |

|   | 1.3    | Operation Parameters                                    | 4    |

|   | 1.4    | On-Chip Memory and Memory Protection                    | 5    |

|   | 1.5    | Interrupt Controller                                    | . 5  |

|   | 1.6    | Peripheral highlights                                   | . 6  |

|   | 1.7    | Block diagrams                                          | 10   |

| 2 | MC5    | 6F826xx signal and pin descriptions                     | 13   |

|   | 2.1    | Signal groups                                           | 18   |

| 3 | Order  | ring parts                                              | 19   |

|   | 3.1    | Determining valid orderable parts                       | 19   |

| 4 | Part i | dentification                                           | 19   |

|   | 4.1    | Description                                             | . 19 |

|   | 4.2    | Format                                                  | . 19 |

|   | 4.3    | Fields                                                  | . 19 |

|   | 4.4    | Example                                                 | 20   |

| 5 | Term   | inology and guidelines                                  | 20   |

|   | 5.1    | Definition: Operating requirement                       | 20   |

|   | 5.2    | Definition: Operating behavior                          | . 21 |

|   | 5.3    | Definition: Attribute                                   | 21   |

|   | 5.4    | Definition: Rating                                      | 21   |

|   | 5.5    | Result of exceeding a rating                            | 22   |

|   | 5.6    | Relationship between ratings and operating requirements | 22   |

|   | 5.7    | Guidelines for ratings and operating requirements       | . 23 |

|   | 5.8    | Definition: Typical value                               | . 23 |

|   | 5.9    | Typical value conditions                                | . 24 |

| 6 | Ratin  | gs                                                      | 25   |

|    | 6.1    | Thermal handling ratings                   |

|----|--------|--------------------------------------------|

|    | 6.2    | Moisture handling ratings25                |

|    | 6.3    | ESD handling ratings                       |

|    | 6.4    | Voltage and current operating ratings      |

| 7  | Gener  | ral                                        |

|    | 7.1    | General characteristics                    |

|    | 7.2    | AC electrical characteristics              |

|    | 7.3    | Nonswitching electrical specifications     |

|    | 7.4    | Switching specifications                   |

|    | 7.5    | Thermal specifications                     |

| 8  | Periph | neral operating requirements and behaviors |

|    | 8.1    | Core modules                               |

|    | 8.2    | System modules                             |

|    | 8.3    | Clock modules                              |

|    | 8.4    | Memories and memory interfaces             |

|    | 8.5    | Analog                                     |

|    | 8.6    | Timer                                      |

|    | 8.7    | Communication interfaces                   |

| 9  | Desig  | n Considerations                           |

|    | 9.1    | Thermal design considerations              |

|    | 9.2    | Electrical design considerations           |

|    | 9.3    | Power-on Reset design considerations       |

| 10 | Obtain | ning package dimensions                    |

| 11 | Pinou  | t                                          |

|    | 11.1   | Signal Multiplexing and Pin Assignments55  |

|    | 11.2   | Pinout diagrams                            |

| 12 | Produ  | ct documentation                           |

# 1 Overview

# 1.1 MC56F826xx Product Family

The following table is the comparsion of features among members of the family.

| Feature                                     |         | MC56F82 |         |

|---------------------------------------------|---------|---------|---------|

| Part Number                                 | 646VLF  | 643VLC  | 623VLC  |

| Core frequency (MHz)                        | 100/50  | 100/50  | 100/50  |

| Flash memory (KB)                           | 64      | 64      | 32      |

| RAM (KB)                                    | 8       | 8       | 8       |

| Interrupt Controller                        | Yes     | Yes     | Yes     |

| Windowed Computer Operating Properly (WCOP) | 1       | 1       | 1       |

| External Watchdog Monitor (EWM)             | 1       | 1       | 1       |

| Periodic Interrupt Timer (PIT)              | 2       | 2       | 2       |

| Cyclic Redundancy Check (CRC)               | 1       | 1       | 1       |

| Quad Timer (TMR)                            | 1x4     | 1x4     | 1x4     |

| 12-bit Cyclic ADC channels                  | 2x5     | 2x3     | 2x3     |

| PWM Module:                                 |         |         |         |

| Input capture channels <sup>1</sup>         | 6       | 6       | 6       |

| Standard channels                           | 6       | 6       | 6       |

| DMA                                         | Yes     | Yes     | Yes     |

| Analog Comparators (CMP)                    | 4       | 3       | 3       |

| QSCI                                        | 2       | 1       | 1       |

| GPIO                                        | 39      | 26      | 26      |

| Package pin count                           | 48 LQFP | 32 LQFP | 32 LQFP |

#### Table 1. MC56F826xx Family

1. Input capture shares the pin with cooresponding PWM channels.

# 1.2 56800EX 32-bit Digital Signal Controller (DSC) core

- Efficient 32-bit 56800EX Digital Signal Processor (DSP) engine with modified dual Harvard architecture:

- Three internal address buses

- Four internal data buses: two 32-bit primary buses, one 16-bit secondary data bus, and one 16-bit instruction bus

- 32-bit data accesses

#### Overview

- Supports concurrent instruction fetches in the same cycle, and dual data accesses in the same cycle

- 20 addressing modes

- As many as 100 million instructions per second (MIPS) at 100 MHz core frequency

- 162 basic instructions

- Instruction set supports both fractional arithmetic and integer arithmetic

- 32-bit internal primary data buses support 8-bit, 16-bit, and 32-bit data movement, plus addition, subtraction, and logical operations

- Single-cycle 16 × 16-bit -> 32-bit and 32 x 32-bit -> 64-bit multiplier-accumulator (MAC) with dual parallel moves

- 32-bit arithmetic and logic multi-bit shifter

- Four 36-bit accumulators, including extension bits

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Bit reverse address mode, which effectively supports DSP and Fast Fourier Transform algorithms

- Full shadowing of the register stack for zero-overhead context saves and restores: nine shadow registers correspond to nine address registers (R0, R1, R2, R3, R4, R5, N, N3, M01)

- Instruction set supports both DSP and controller functions

- Controller-style addressing modes and instructions enable compact code

- Enhanced bit manipulation instruction set

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack, with the stack's depth limited only by memory

- Priority level setting for interrupt levels

- JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, real-time debugging that is independent of processor speed

# **1.3 Operation Parameters**

- Up to 50 MHz operation in normal mode and 100 MHz operation in fast mode

- Operation ambient temperature:

- -40 °C to 105°C

- Single 3.3 V power supply

- Supply range:  $V_{DD}$   $V_{SS}$  = 2.7 V to 3.6 V,  $V_{DDA}$   $V_{SSA}$  = 2.7 V to 3.6 V

## **1.4 On-Chip Memory and Memory Protection**

- Dual Harvard architecture permits as many as three simultaneous accesses to program and data memory

- Internal flash memory with security and protection to prevent unauthorized access

- Memory resource protection (MRP) unit to protect supervisor programs and resources from user programs

- Programming code can reside in flash memory during flash programming

- The dual-port RAM controller supports concurrent instruction fetches and data accesses, or dual data accesses by the core.

- Concurrent accesses provide increased performance.

- The data and instruction arrive at the core in the same cycle, reducing latency.

- On-chip memory

- Up to 64 KB program/data flash memory

- 8 KB dual port data/program RAM

# 1.5 Interrupt Controller

- Five interrupt priority levels

- Three user-programmable priority levels for each interrupt source: level 0, level 1, level 2

- Unmaskable level 3 interrupts include illegal instruction, hardware stack overflow, misaligned data access, SWI3 instruction

- Interrupt level 3 is highest priority and non-maskable. Its sources include:

- Illegal instructions

- Hardware stack overflow

- SWI instruction

- EOnce interrupts

- Misaligned data accesses

- Lowest-priority software interrupt: level LP

- Support for nested interrupts, so that a higher priority level interrupt request can interrupt lower priority interrupt subroutine

- Masking of interrupt priority level is managed by the 56800EX core

- Two programmable fast interrupts that can be assigned to any interrupt source

- Notification to System Integration Module (SIM) to restart clock when in wait and stop states

- Ability to relocate interrupt vector table

# 1.6 Peripheral highlights

#### 1.6.1 Flex Pulse Width Modulator (FlexPWM)

- Up to 100 MHz operation clock with PWM Resolution as fine as 10 ns

- PWM module contains four identical submodules, with two outputs per submodule

- 16 bits of resolution for center, edge-aligned, and asymmetrical PWMs

- PWM outputs can be configured as complementary output pairs or independent outputs

- Dedicated time-base counter with period and frequency control per submodule

- Independent top and bottom deadtime insertion for each complementary pair

- Independent control of both edges of each PWM output

- Enhanced input capture and output compare functionality on each input:

- Channels not used for PWM generation can be used for buffered output compare functions.

- Channels not used for PWM generation can be used for input capture functions.

- Enhanced dual edge capture functionality

- Synchronization of submodule to external hardware (or other PWM) is supported.

- Double-buffered PWM registers

- Integral reload rates from 1 to 16

- Half-cycle reload capability

- Multiple output trigger events can be generated per PWM cycle via hardware.

- Support for double-switching PWM outputs

- Up to eight fault inputs can be assigned to control multiple PWM outputs

- Programmable filters for fault inputs

- Independently programmable PWM output polarity

- Individual software control of each PWM output

- All outputs can be programmed to change simultaneously via a FORCE\_OUT event.

- Option to supply the source for each complementary PWM signal pair from any of the following:

- Crossbar module outputs

- External ADC input, taking into account values set in ADC high and low limit registers

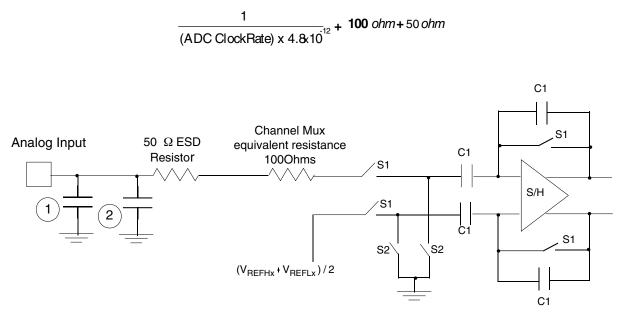

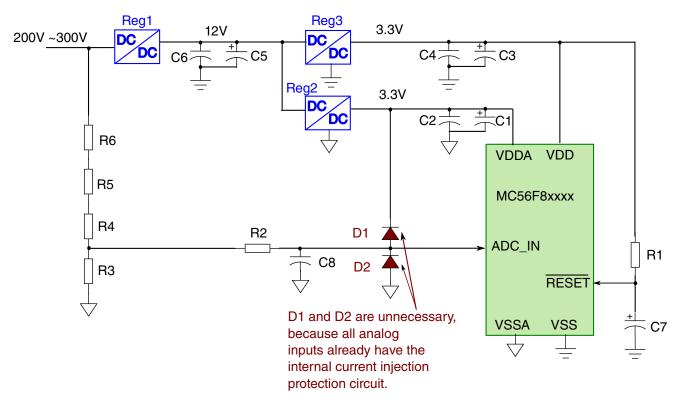

### 1.6.2 12-bit Analog-to-Digital Converter (Cyclic type)

- Two independent 12-bit analog-to-digital converters (ADCs):

- 2 x 5-channel external inputs

- Built-in x1, x2, x4 programmable gain pre-amplifier

- Maximum ADC clock frequency up to 10 MHz, having period as low as 100-ns

- Single conversion time of 10 ADC clock cycles

- Additional conversion time of 8 ADC clock cycles

- Support of analog inputs for single-ended and differential, including unipolar differential, conversions

- Sequential, parallel, and independent scan mode

- First 8 samples have offset, limit and zero-crossing calculation supported

- ADC conversions can be synchronized by *any* module connected to the internal crossbar module, such as PWM, timer, GPIO, and comparator modules.

- Support for simultaneous triggering and software-triggering conversions

- Support for a multi-triggering mode with a programmable number of conversions on each trigger

- Each ADC has ability to scan and store up to 8 conversion results.

- Current injection protection

## 1.6.3 Periodic Interrupt Timer (PIT) Modules

- 16-bit counter with programmable count modulo

- PIT0 is master and PIT1 is slave (if synchronizing both PITs)

- The output signals of both PIT0 and PIT1 are internally connected to a peripheral crossbar module

- Can run when the CPU is in Wait/Stop modes. Can also wake up the CPU from Wait/Stop modes.

- In addition to its existing bus clock (up to 50 MHz), 3 alternate clock sources for the counter clock are available:

- Crystal oscillator output

- 8 MHz / 400 kHz ROSC (relaxation oscillator output)

- On-chip low-power 200 kHz oscillator

# 1.6.4 Inter-Module Crossbar and AND-OR-INVERT logic

- Provides generalized connections between and among on-chip peripherals: ADCs, comparators, quad-timers, FlexPWMs, EWM, and select I/O pins

- User-defined input/output pins for all modules connected to the crossbar

- DMA request and interrupt generation from the crossbar

- Write-once protection for all registers

- AND-OR-INVERT function provides a universal Boolean function generator that uses a four-term sum-of-products expression, with each product term containing true or complement values of the four selected inputs (A, B, C, D).

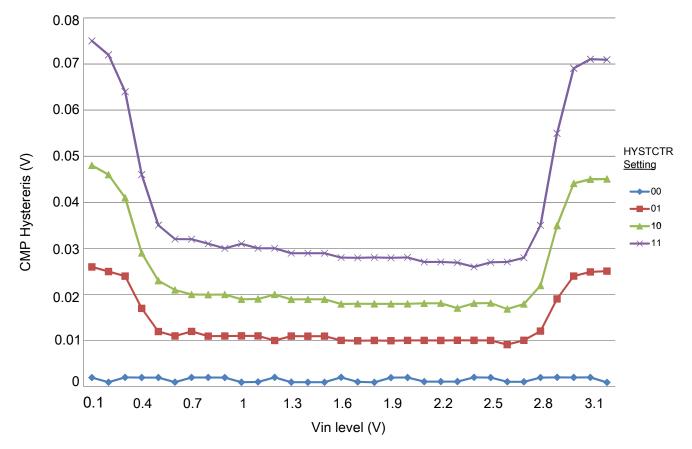

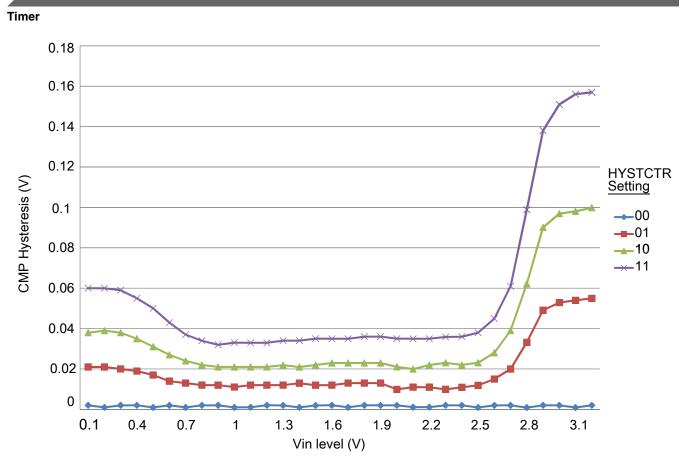

### 1.6.5 Comparator

- Full rail-to-rail comparison range

- Support for high and low speed modes

- Selectable input source includes external pins and internal DACs

- Programmable output polarity

- 6-bit programmable DAC as a voltage reference per comparator

- Three programmable hysteresis levels

- Selectable interrupt on rising-edge, falling-edge, or toggle of a comparator output

### 1.6.6 Quad Timer

- Four 16-bit up/down counters, with a programmable prescaler for each counter

- Operation modes: edge count, gated count, signed count, capture, compare, PWM, signal shot, single pulse, pulse string, cascaded, quadrature decode

- Programmable input filter

- Counting start can be synchronized across counters

- Up to 100 MHz operation clock

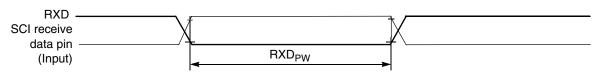

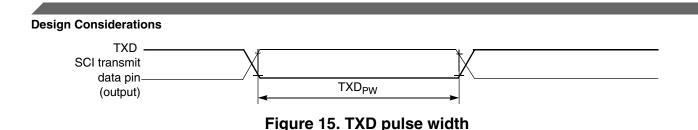

### **1.6.7** Queued Serial Communications Interface (QSCI) modules

- Operating clock can be up to two times the CPU operating frequency

- Four-word-deep FIFOs available on both transmit and receive buffers

- Standard mark/space non-return-to-zero (NRZ) format

- 16-bit integer and 3-bit fractional baud rate selection

- Full-duplex or single-wire operation

- Programmable 8-bit or 9-bit data format

- Error detection capability

- Two receiver wakeup methods:

- Idle line

- Address mark

- 1/16 bit-time noise detection

- Up to 6.25 Mbit/s baud rate at 100 MHz operation clock

### 1.6.8 Windowed Computer Operating Properly (COP) watchdog

- Programmable windowed timeout period

- Support for operation in all power modes: run mode, wait mode, stop mode

- Causes loss of reference reset 128 cycles after loss of reference clock to the PLL is detected

- Selectable reference clock source in support of EN60730 and IEC61508

- Selectable clock sources:

- External crystal oscillator/external clock source

- On-chip low-power 200 kHz oscillator

- System bus (IPBus up to 50 MHz)

- 8 MHz / 400 kHz ROSC

- Support for interrupt triggered when the counter reaches the timeout value

### 1.6.9 External Watchdog Monitor (EWM)

- Monitors external circuit as well as the software flow

- Programmable timeout period

- Interrupt capability prior to timeout

- Independent output (EWM\_OUT\_b) that places external circuit (but not CPU and peripheral) in a safe mode when EWM timeout occurs

- Selectable reference clock source in support of EN60730 and IEC61508

- Wait mode and Stop mode operation is not supported.

- Selectable clock sources:

- External crystal oscillator/external clock source

- On-chip low-power 200 kHz oscillator

- System bus (IPBus up to 50 MHz)

- 8 MHz / 400 kHz ROSC

### 1.6.10 Power supervisor

- Power-on reset (POR) is released after VDD > 2.7 V during supply is ramped up; CPU, peripherals, and JTAG/EOnCE controllers exit RESET state

- Brownout reset ( $V_{DD} < 2.0 \text{ V}$ )

- Critical warn low-voltage interrupt (LVI 2.2 V)

- Peripheral low-voltage warning interrupt (LVI 2.7 V)

### 1.6.11 Phase-locked loop

- Wide programmable output frequency: 200 MHz to 400 MHz

- Input reference clock frequency: 8 MHz to 16 MHz

- Detection of loss of lock and loss of reference clock

- Ability to power down

### 1.6.12 Clock sources

#### 1.6.12.1 On-chip oscillators

- Tunable 8 MHz relaxation oscillator with 400 kHz at standby mode (divide-by-two output)

- 200 kHz low frequency clock as secondary clock source for COP, EWM, PIT

#### 1.6.12.2 Crystal oscillator

- Support for both high ESR crystal oscillator (ESR greater than 100  $\Omega$ ) and ceramic resonator

- Operating frequency: 4–16 MHz

### 1.6.13 Cyclic Redundancy Check (CRC) Generator

- Hardware CRC generator circuit with 16-bit shift register

- High-speed hardware CRC calculation

- Programmable initial seed value

- CRC16-CCITT compliancy with  $x^{16} + x^{12} + x^5 + 1$  polynomial

- Error detection for all single, double, odd, and most multibit errors

- Option to transpose input data or output data (CRC result) bitwise, which is required for certain CRC standards

### 1.6.14 General Purpose I/O (GPIO)

- 5 V tolerance (except RESETB pin)

- Individual control of peripheral mode or GPIO mode for each pin

- Programmable push-pull or open drain output

- Configurable pullup or pulldown on all input pins

- All pins (except JTAG and RESETB) default to be GPIO inputs

- 2 mA / 9 mA source/sink capability

- Controllable output slew rate

## 1.7 Block diagrams

The 56800EX core is based on a modified dual Harvard-style architecture, consisting of three execution units operating in parallel, and allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set

enable straightforward generation of efficient and compact code for the DSP and control functions. The instruction set is also efficient for C compilers, to enable rapid development of optimized control applications.

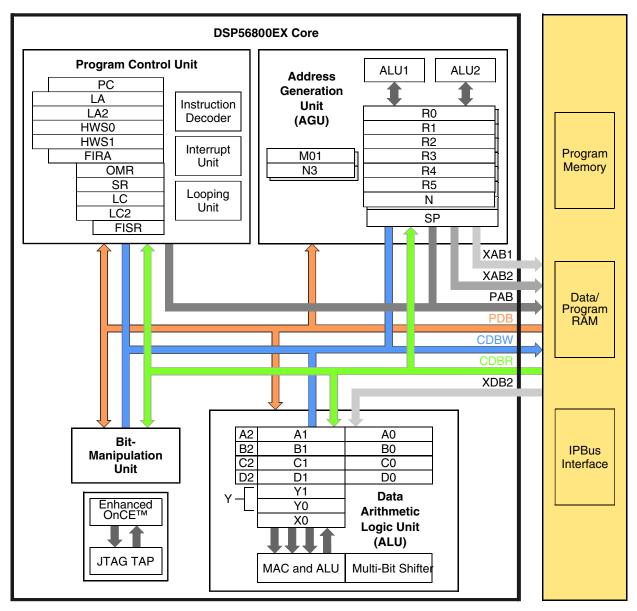

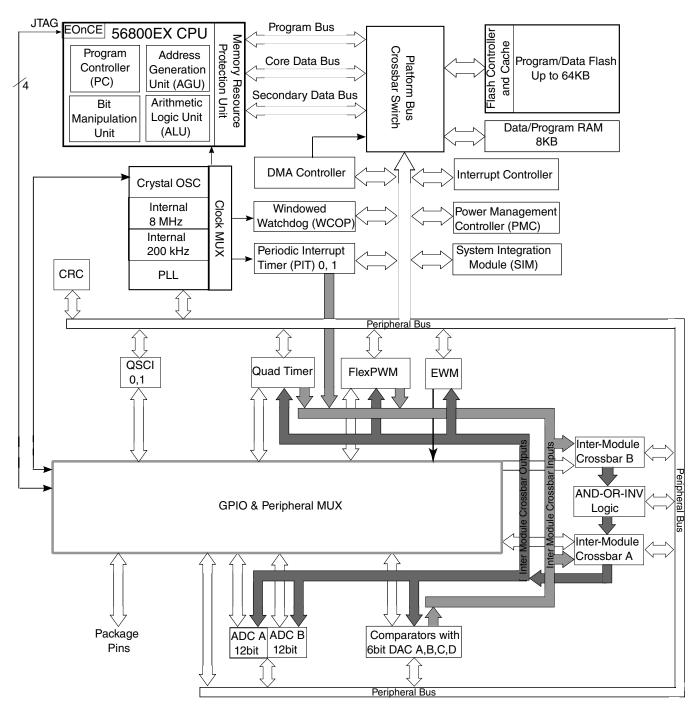

The device's basic architecture appears in Figure 1 and Figure 2. Figure 1 shows how the 56800EX system buses communicate with internal memories, and the IPBus interface and the internal connections among the units of the 56800EX core. Figure 2 shows the peripherals and control blocks connected to the IPBus bridge. See the specific device's Reference Manual for details.

Figure 1. 56800EX basic block diagram

Figure 2. System diagram

After reset, each pin is configured for its primary function (listed first). Any alternative functionality, shown in parentheses, must be programmed through the GPIO module peripheral enable registers (GPIOx\_PER) and the SIM module GPIO peripheral select (GPSx) registers. All GPIO ports can be individually programmed as an input or output (using bit manipulation).

• PWMA\_FAULT0, PWMA\_FAULT1, and similar signals are inputs used to disable selected PWMA outputs, in cases where the fault conditions originate off-chip.

For the MC56F826xx products, which use 48-pin LQFP and 32-pin packages:

| Signal Name      | 48 LQFP | 32 LQFP             | Туре             | State During<br>Reset                                                                                      | Signal Description                                                                                                                                                             |  |

|------------------|---------|---------------------|------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>DD</sub>  | 32      | —                   | Supply           | Supply                                                                                                     | I/O Power — Supplies 3.3 V power to the                                                                                                                                        |  |

|                  | 44      | 28                  |                  |                                                                                                            | chip I/O interface.                                                                                                                                                            |  |

| V <sub>SS</sub>  | 22      | 14                  | Supply           | Supply                                                                                                     | I/O Ground — Provide ground for the device                                                                                                                                     |  |

|                  | 31      | —                   |                  |                                                                                                            | I/O interface.                                                                                                                                                                 |  |

|                  | 45      | 29                  |                  |                                                                                                            |                                                                                                                                                                                |  |

| V <sub>DDA</sub> | 15      | 9                   | Supply           | Supply                                                                                                     | Analog Power — Supplies 3.3 V power to<br>the analog modules. It must be connected to<br>a clean analog power supply.                                                          |  |

| V <sub>SSA</sub> | 16      | 10                  | Supply           | Supply                                                                                                     | Analog Ground — Supplies an analog<br>ground to the analog modules. It must be<br>connected to a clean power supply.                                                           |  |

| V <sub>CAP</sub> | 19      | —                   | On-chip          | On-chip                                                                                                    | Connect a 2.2 µF bypass capacitor betweer                                                                                                                                      |  |

|                  | 43 27   | regulator<br>output | regulator output | this pin and $V_{SS}$ to stabilize the core voltage regulator output required for proper device operation. |                                                                                                                                                                                |  |

|                  |         |                     |                  |                                                                                                            | NOTE: The total bypass capacitor value<br>between all V <sub>CAP</sub> pin and V <sub>SS</sub><br>should <b>not</b> exceed 4.7 μF.                                             |  |

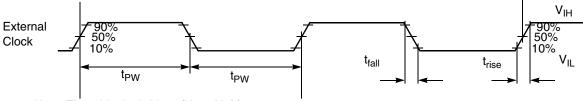

| TDI              | 48      | 32                  | Input            | Input, internal pullup enabled                                                                             | Test Data Input — It is sampled on the rising edge of TCK and has an internal pullup resistor. After reset, the default state is TDI.                                          |  |

| (GPIOD0)         |         |                     | Input/Output     |                                                                                                            | GPIO Port D0                                                                                                                                                                   |  |

| TDO              | 46      | 30                  | Output           | Output                                                                                                     | Test Data Output — It is driven in the shift-IR<br>and shift-DR controller states, and it changes<br>on the falling edge of TCK. After reset, the<br>default state is TDO      |  |

| (GPIOD1)         |         |                     | Input/Output     | Output                                                                                                     | GPIO Port D1                                                                                                                                                                   |  |

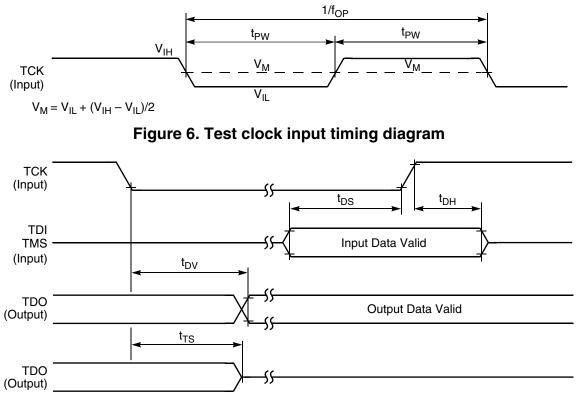

| тск              | 1       | 1                   | Input            | Input, internal<br>pulldown<br>enabled                                                                     | Test Clock Input — The pin is connected<br>internally to a pulldown resistor. A Schmitt-<br>trigger input is used for noise immunity. After<br>reset, the default state is TCK |  |

#### Table 2. Signal descriptions

Table continues on the next page ...

#### MC56F826xx, Rev. 0, 08/2018

| Table 2. | Signal | descriptions | (continued) |

|----------|--------|--------------|-------------|

|----------|--------|--------------|-------------|

| Signal Name                | 48 LQFP | 32 LQFP | Туре                          | State During<br>Reset             | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|----------------------------|---------|---------|-------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (GPIOD2)                   |         |         | Input/Output                  |                                   | GPIO Port D2                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| TMS                        | 47      | 31      | Input                         | Input, internal<br>pullup enabled | Test Mode Select Input — It is sampled on<br>the rising edge of TCK and has an internal<br>pullup resistor. After reset, the default state<br>is TMS.                                                                                                                                                                                                                                                                                           |  |

|                            |         |         |                               |                                   | <b>NOTE:</b> Always tie the TMS pin to $V_{DD}$<br>through a 2.2 k $\Omega$ resistor if need to<br>keep on-board debug capability.<br>Otherwise, directly tie to $V_{DD}$ .                                                                                                                                                                                                                                                                     |  |

| (GPIOD3)                   |         |         | Input/Output                  |                                   | GPIO Port D3                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| RESET or RESETB            | 2       | 2       | Input                         | Input, internal<br>pullup enabled | Reset — A direct hardware reset on the<br>processor. When RESET is asserted low,<br>the device is initialized and placed in the<br>reset state. A Schmitt-trigger input is used<br>for noise immunity. The internal reset signal<br>is deasserted synchronous with the internal<br>clocks after a fixed number of internal clock<br>After reset, the default state is RESET.<br>Recommended a capacitor of up to 0.1 μF<br>for filtering noise. |  |

| (GPIOD4)                   |         |         | Input/<br>Opendrain<br>Output |                                   | GPIO Port D4 RESET functionality is<br>disabled in this mode and the device can be<br>reset only through POR, COP reset, or<br>software reset.                                                                                                                                                                                                                                                                                                  |  |

| GPIOA0                     | 9       | 6       | Input/Output                  | Input                             | GPIO Port A0                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| (ANA0&CMPA_IN3)            |         |         | Input                         |                                   | ANA0 is analog input to channel 0 of ADCA;<br>CMPA_IN3 is positive input 3 of analog<br>comparator A. After reset, the default state is<br>GPIOA0.                                                                                                                                                                                                                                                                                              |  |

| (CMPC_O)                   |         |         | Output                        |                                   | Analog comparator C output                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| GPIOA1                     | 10      | 7       | Input/Output                  | Input                             | GPIO Port A1: After reset, the default state is GPIOA1.                                                                                                                                                                                                                                                                                                                                                                                         |  |

| (ANA1&CMPA_IN0)            | 1       |         | Input                         |                                   | ANA1 is analog input to channel 1 of ADCA;<br>CMPA_IN0 is negative input 0 of analog<br>comparator A. When used as an analog<br>input, the signal goes to ANA1 and<br>CMPA_IN0. The ADC control register<br>configures this input as ANA1 or CMPA_IN0.                                                                                                                                                                                          |  |

| GPIOA2                     | 11      | 8       | Input/Output                  | Input                             | GPIO Port A2: After reset, the default state is GPIOA2.                                                                                                                                                                                                                                                                                                                                                                                         |  |

| (ANA2&VREFHA&C<br>MPA_IN1) |         |         | Input                         |                                   | ANA2 is analog input to channel 2 of ADCA;<br>VREFHA is analog reference high of ADCA;<br>CMPA_IN1 is negative input 1 of analog<br>comparator A. When used as an analog<br>input, the signal goes to both ANA2,<br>VREFHA, and CMPA_IN1.                                                                                                                                                                                                       |  |

| GPIOA3                     | 12      | —       | Input/Output                  | Input                             | GPIO Port A3: After reset, the default state is GPIOA3.                                                                                                                                                                                                                                                                                                                                                                                         |  |

Table continues on the next page ...

| Signal Name                | 48 LQFP | 32 LQFP | Туре         | State During<br>Reset | Signal Description                                                                                                                                                                                                                         |

|----------------------------|---------|---------|--------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (ANA3&VREFLA&C<br>MPA_IN2) |         |         | Input        |                       | ANA3 is analog input to channel 3 of ADCA;<br>VREFLA is analog reference low of ADCA;<br>CMPA_IN2 is negative input 2 of analog<br>comparator A.                                                                                           |

| GPIOA4                     | 8       | —       | Input/Output | Input                 | GPIO Port A4: After reset, the default state is GPIOA4.                                                                                                                                                                                    |

| (ANA4&CMPD_IN0)            |         |         | Input        |                       | ANA4 is Analog input to channel 4 of ADCA;<br>CMPD_IN0 is input 0 to comparator D.                                                                                                                                                         |

| GPIOB0                     | 17      | 11      | Input/Output | Input                 | GPIO Port B0: After reset, the default state is GPIOB0.                                                                                                                                                                                    |

| (ANB0&CMPB_IN3)            |         |         | Input        |                       | ANB0 is analog input to channel 0 of ADCB;<br>CMPB_IN3 is positive input 3 of analog<br>comparator B. When used as an analog<br>input, the signal goes to ANB0 and<br>CMPB_IN3. The ADC control register<br>configures this input as ANB0. |

| GPIOB1                     | 18      | 12      | Input/Output | Input                 | GPIO Port B1: After reset, the default state is GPIOB1.                                                                                                                                                                                    |

| (ANB1&CMPB_IN0)            |         |         | Input        |                       | ANB1 is analog input to channel 1 of ADCB;<br>CMPB_IN0 is negative input 0 of analog<br>comparator B. When used as an analog<br>input, the signal goes to ANB1 and<br>CMPB_IN0. The ADC control register<br>configures this input as ANB1. |

| GPIOB2                     | 20      | 13      | Input/Output | Input                 | GPIO Port B2: After reset, the default state is GPIOB2.                                                                                                                                                                                    |

| (ANB2&VERFHB&C<br>MPC_IN3) |         |         | Input        |                       | ANB2 is analog input to channel 2 of ADCB;<br>VREFHB is analog reference high of ADCB;<br>CMPC_IN3 is positive input 3 of analog<br>comparator C. When used as an analog<br>input, the signal goes to both ANB2 and<br>CMPC_IN3.           |

| GPIOB3                     | 21      |         | Input/Output | Input                 | GPIO Port B3: After reset, the default state is GPIOB3.                                                                                                                                                                                    |

| (ANB3&VREFLB&C<br>MPC_IN0) |         |         | Input        |                       | ANB3 is analog input to channel 3 of ADCB;<br>VREFLB is analog reference low of ADCB;<br>CMPC_IN0 is negative input 0 of analog<br>comparator C.                                                                                           |

| GPIOB4                     | 14      |         | Input/Output | Input                 | GPIO Port B4: After reset, the default state is GPIOB4.                                                                                                                                                                                    |

| (ANB4&CMPC_IN1)            | -       |         | Input        |                       | ANB4 is analog input to channel 4 of ADCB;<br>CMPC_IN1 is negative input 1 of analog<br>comparator C.                                                                                                                                      |

| GPIOC0                     | 3       | —       | Input/Output | Input                 | GPIO Port C0: After reset, the default state is GPIOC0.                                                                                                                                                                                    |

| (EXTAL)                    |         |         | Analog Input |                       | The external crystal oscillator input (EXTAL) connects the internal crystal oscillator input to an external crystal or ceramic resonator.                                                                                                  |

Table 2. Signal descriptions (continued)

Table continues on the next page ...

| Signal Name | 48 LQFP | 32 LQFP | Туре         | State During<br>Reset | Signal Description                                                                                                                                        |

|-------------|---------|---------|--------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| (CLKIN0)    |         |         | Input        |                       | External clock input 0 <sup>1</sup>                                                                                                                       |

| GPIOC1      | 4       | -       | Input/Output | Input                 | GPIO Port C1: After reset, the default state is GPIOC1.                                                                                                   |

| (XTAL)      |         |         | Input        |                       | The external crystal oscillator output (XTAL) connects the internal crystal oscillator output to an external crystal or ceramic resonator.                |

| GPIOC2      | 5       | 3       | Input/Output | Input                 | GPIO Port C2: After reset, the default state is GPIOC2.                                                                                                   |

| (TXD0)      |         |         | Output       |                       | SCI0 transmit data output or transmit/receive in single wire operation                                                                                    |

| (XB_OUT11)  |         |         | Output       | -                     | Crossbar module output 11                                                                                                                                 |

| (XB_IN2)    |         |         | Input        |                       | Crossbar module input 2                                                                                                                                   |

| (CLKO0)     |         |         | Output       |                       | Buffered clock output 0: the clock source is<br>selected by clockout select (CLKOSEL) bits<br>in the clock output select register (CLKOUT)<br>of the SIM. |

| GPIOC3      | 6       | 4       | Input/Output | Input                 | GPIO Port C3: After reset, the default state is GPIOC3.                                                                                                   |

| (TA0)       |         |         | Input/Output |                       | Quad timer module A channel 0 input/output                                                                                                                |

| (CMPA_O)    |         |         | Output       |                       | Analog comparator A output                                                                                                                                |

| (RXD0)      |         |         | Input        |                       | SCI0 receive data input                                                                                                                                   |

| (CLKIN1)    |         |         | Input        |                       | External clock input 1                                                                                                                                    |

| GPIOC4      | 7       | 5       | Input/Output | Input                 | GPIO Port C4: After reset, the default state is GPIOC4.                                                                                                   |

| (TA1)       |         |         | Input/Output |                       | Quad timer module A channel 1 input/output                                                                                                                |

| (CMPB_O)    |         |         | Output       |                       | Analog comparator B output                                                                                                                                |

| (XB_IN6)    |         |         | Input        |                       | Crossbar module input 6                                                                                                                                   |

| (EWM_OUT_B) |         |         | Output       | -                     | External Watchdog Module output                                                                                                                           |

| GPIOC5      | 13      | -       | Input/Output | Input                 | GPIO Port C5: After reset, the default state is GPIOC5.                                                                                                   |

| (XB_IN7)    |         |         | Input        | -                     | Crossbar module input 7                                                                                                                                   |

| GPIOC6      | 23      | 15      | Input/Output | Input                 | GPIO Port C6: After reset, the default state is GPIOC6.                                                                                                   |

| (TA2)       |         |         | Input/Output |                       | Quad timer module A channel 2 input/output                                                                                                                |

| (XB_IN3)    |         |         | Input        |                       | Crossbar module input 3                                                                                                                                   |

| (CMP_REF)   |         |         | Analog Input |                       | Positive input 3 of analog comparator A and B and C.                                                                                                      |

| GPIOC7      | 24      | -       | Input/Output | Input                 | GPIO Port C7: After reset, the default state is GPIOC7.                                                                                                   |

| (TXD0)      |         |         | Output       | ]                     | SCI0 transmit data output or transmit/receive in single wire operation                                                                                    |

| (XB_IN8)    |         |         | Input        | ]                     | Crossbar module input 8                                                                                                                                   |

Table continues on the next page ...

| Signal Name  | 48 LQFP | 32 LQFP | Туре         | State During<br>Reset | Signal Description                                                     |

|--------------|---------|---------|--------------|-----------------------|------------------------------------------------------------------------|

| GPIOC8       | 25      | 16      | Input/Output | Input                 | GPIO Port C8: After reset, the default state is GPIOC8.                |

| (RXD0)       |         |         | Input        |                       | SCI0 receive data input                                                |

| (XB_IN9)     |         |         | Input        |                       | Crossbar module input 9                                                |

| (XB_OUT6)    |         |         | Output       |                       | Crossbar module output 6                                               |

| GPIOC9       | 26      | 17      | Input/Output | Input                 | GPIO Port C9: After reset, the default state is GPIOC9.                |

| (XB_IN4)     |         |         | Input        | -                     | Crossbar module input 4                                                |

| (TXD0)       |         |         | Output       |                       | SCI0 transmit data output or transmit/receive in single wire operation |

| (XB_OUT8)    |         |         | Output       |                       | Crossbar module output 8                                               |

| GPIOC10      | 27      | 18      | Input/Output | Input                 | GPIO Port C10: After reset, the default state is GPIOC10.              |

| (XB_IN5)     |         |         | Input        |                       | Crossbar module input 4                                                |

| (XB_OUT9)    |         |         | Output       |                       | Crossbar module output 9                                               |

| GPIOC11      | 29      | _       | Input/Output | Input                 | GPIO Port C11: After reset, the default state is GPIOC11.              |

| (TXD1)       |         |         | Output       |                       | SCI1 transmit data output or transmit/receive in single wire operation |

| GPIOC12      | 30      | -       | Input/Output | Input                 | GPIO Port C12: After reset, the default state is GPIOC12.              |

| (RXD1)       |         |         | Input        |                       | SCI1 receive data input                                                |

| GPIOC13      | 37      | -       | Input/Output | Input                 | GPIO Port C13: After reset, the default state is GPIOC13.              |

| (TA3)        |         |         | Input/Output |                       | Quad timer module A channel 3 input/output                             |

| (XB_IN6)     |         |         | Input        |                       | Crossbar module input 6                                                |

| (EWM_OUT_B)  |         |         | Output       |                       | External Watchdog Module output                                        |

| GPIOC14      | 41      | -       | Input/Output | Input                 | GPIO Port C14: After reset, the default state is GPIOC14.              |

| (XB_OUT4)    |         |         | Output       |                       | Crossbar module output 4                                               |

| (PWM_FAULT4) |         |         | Input        | -                     | Disable PWMA output 4                                                  |

| GPIOC15      | 42      | -       | Input/Output | Input                 | GPIO Port C15: After reset, the default state is GPIOC15.              |

| (XB_OUT5)    |         |         | Output       |                       | Crossbar module output 5                                               |

| (PWM_FAULT5) |         |         | Input        |                       | Disable PWMA output 5                                                  |

| GPIOE0       | 33      | 21      | Input/Output | Input                 | GPIO Port E0: After reset, the default state is GPIOE0.                |

| (PWM_0B)     |         |         | Input/Output |                       | PWM module A , submodule 0, output B or input capture B                |

| GPIOE1       | 34      | 22      | Input/Output | Input                 | GPIO Port E1: After reset, the default state is GPIOE1.                |

| (PWM_0A)     |         |         | Input/Output | ]                     | PWM module A , submodule 0, output A or input capture A                |

Table 2. Signal descriptions (continued)

Table continues on the next page ...

#### MC56F826xx, Rev. 0, 08/2018

| Signal Name | 48 LQFP | 32 LQFP | Туре         | State During<br>Reset | Signal Description                                                                                                                                        |

|-------------|---------|---------|--------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOE2      | 35      | 23      | Input/Output | Input                 | GPIO Port E2: After reset, the default state is GPIOE2.                                                                                                   |

| (PWMA_1B)   |         |         | Input/Output |                       | PWM module A , submodule 1, output B or input capture B                                                                                                   |

| GPIOE3      | 36      | 24      | Input/Output | Input                 | GPIO Port E3: After reset, the default state is GPIOE3.                                                                                                   |

| (PWMA_1A)   |         |         | Input/Output |                       | PWM module A , submodule 1, output A or input capture A                                                                                                   |

| GPIOE4      | 39      | 25      | Input/Output | Input                 | GPIO Port E4: After reset, the default state is GPIOE4.                                                                                                   |

| (PWMA_2B)   |         |         | Input/Output |                       | PWM module A , submodule 2, output B or input capture B                                                                                                   |

| (XB_IN2)    |         |         | Input        |                       | Crossbar module input 2                                                                                                                                   |

| GPIOE5      | 40      | 26      | Input/Output | Input                 | GPIO Port E5: After reset, the default state is GPIOE5.                                                                                                   |

| (PWMA_2A)   |         |         | Input/Output |                       | PWM module A , submodule 2, output A or input capture A                                                                                                   |

| (XB_IN3)    |         |         | Input        |                       | Crossbar module input 3                                                                                                                                   |

| GPIOF0      | 28      | _       | Input/Output | Input                 | GPIO Port F0: After reset, the default state is GPIOF0.                                                                                                   |

| (XB_IN6)    |         |         | Input        |                       | Crossbar module input 6                                                                                                                                   |

| GPIOF1      | 38      | _       | Input/Output | Input                 | GPIO Port F1: After reset, the default state is GPIOF1.                                                                                                   |

| (CLKO1)     |         |         | Output       |                       | Buffered clock output 1: the clock source is<br>selected by clockout select (CLKOSEL) bits<br>in the clock output select register (CLKOUT)<br>of the SIM. |

| (XB_IN7)    |         |         | Input        |                       | Crossbar module input 7                                                                                                                                   |

| (CMPD_O)    |         |         | Output       |                       | Analog comparator D output                                                                                                                                |

| GPIOF2      | —       | 19      | Input/Output | Input                 | GPIO Port F2: After reset, the default state is GPIOF2.                                                                                                   |

| (XB_OUT6)   |         |         | Output       |                       | Crossbar module output 6                                                                                                                                  |

| GPIOF3      | —       | 20      | Input/Output | Input                 | GPIO Port F3: After reset, the default state is GPIOF3.                                                                                                   |

| (XB_OUT7)   |         |         | Output       |                       | Crossbar module output 7                                                                                                                                  |

Table 2. Signal descriptions (continued)

1. If CLKIN is selected as the device's external clock input, then both the GPS\_C0 bit (in GPS1) and the EXT\_SEL bit (in OCCS oscillator control register (OSCTL)) must be set. Also, the crystal oscillator should be powered down.

# 2.1 Signal groups

The input and output signals of the MC56F826xx are organized into functional groups, as detailed in the following table.

#### **Ordering parts**

| Functional Group                                                                     | Numbe  | r of Pins |

|--------------------------------------------------------------------------------------|--------|-----------|

|                                                                                      | 32LQFP | 48LQFP    |

| Power Inputs (V <sub>DD</sub> , V <sub>DDA</sub> ), Power output( V <sub>CAP</sub> ) | 3      | 5         |

| Ground (V <sub>SS</sub> , V <sub>SSA</sub> )                                         | 3      | 4         |

| Reset                                                                                | 1      | 1         |

| FlexPWM ports not including fault pins                                               | 6      | 6         |

| Queued Serial Communications Interface (QSCI0 and QSCI1) ports                       | 4      | 7         |

| 12-bit Analog-to-Digital Converter inputs                                            | 6      | 10        |

| Analog Comparator inputs/outputs                                                     | 7/3    | 11/4      |

| Quad Timer Module (TMRA and TMRB) ports                                              | 3      | 4         |

| Inter-Module Crossbar inputs/outputs                                                 | 8/4    | 12/6      |

| Clock inputs/outputs                                                                 | 1/1    | 2/2       |

| JTAG / Enhanced On-Chip Emulation (EOnCE)                                            | 4      | 4         |

#### Table 3. Functional Group Pin Allocations

# 3 Ordering parts

### 3.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to **nxp.com** and perform a part number search for the following device numbers: MC56F82

# 4 Part identification

## 4.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

## 4.2 Format

Part numbers for this device have the following format: Q 56F8 2 C F P T PP N

# 4.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                                                             | Values                                                                                       |

|-------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Q     | Qualification status                                                    | <ul> <li>MC = Fully qualified, general market flow</li> <li>PC = Prequalification</li> </ul> |

| 56F8  | DSC family with flash memory and DSP56800/<br>DSP56800E/DSP56800EX core | • 56F8                                                                                       |

| 2     | DSC subfamily                                                           | • 2                                                                                          |

| С     | Maximum CPU frequency (MHz)                                             | • 6 = 100 MHz                                                                                |

| F     | Primary program flash memory size                                       | <ul> <li>2 = 32 KB</li> <li>4 = 64 KB</li> </ul>                                             |

| Р     | Pin count                                                               | • 3 = 32<br>• 6 = 48                                                                         |

| Т     | Temperature range (°C)                                                  | • V = -40 to 105                                                                             |

| PP    | Package identifier                                                      | <ul> <li>LC = 32LQFP</li> <li>LF = 48LQFP</li> </ul>                                         |

| N     | Packaging type                                                          | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul>                               |

# 4.4 Example

This is an example part number: MC56F82646VLF

# 5 Terminology and guidelines

# 5.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

### 5.1.1 Example

This is an example of an operating requirement:

Terminology and guidelines

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | 0.9  | 1.1  | V    |

## 5.2 Definition: Operating behavior

Unless otherwise specified, an *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

#### 5.2.1 Example

This is an example of an operating behavior:

| Symbol | Description                                  | Min. | Max. | Unit |

|--------|----------------------------------------------|------|------|------|

| 1 ···· | Digital I/O weak pullup/<br>pulldown current | 10   | 130  | μΑ   |

# 5.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

### 5.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | —    | 7    | pF   |

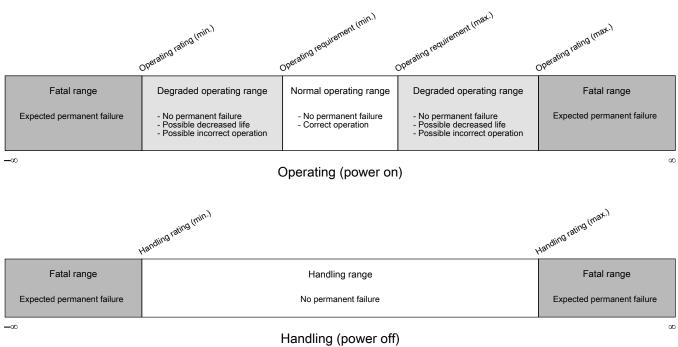

# 5.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- *Handling ratings* apply when the chip is not powered.

#### 5.4.1 Example

This is an example of an operating rating:

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 | 1.2  | V    |

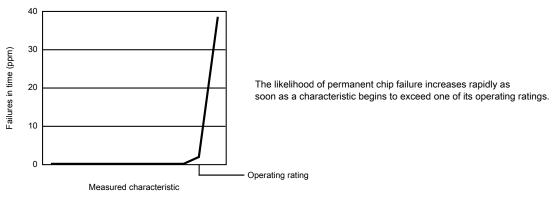

# 5.5 Result of exceeding a rating

Terminology and guidelines

# 5.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

# 5.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

# 5.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

## 5.8.2 Example 2

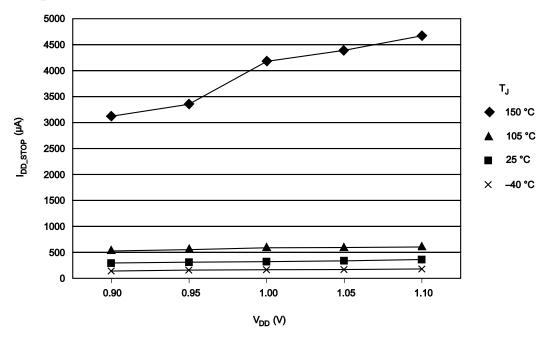

This is an example of a chart that shows typical values for various voltage and temperature conditions:

# 5.9 Typical value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | C°   |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

# 6 Ratings

# 6.1 Thermal handling ratings

| Symbol           | Description                   | Min. | Max. | Unit | Notes |

|------------------|-------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | —    | 260  | °C   | 2     |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

# 6.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level |      | 3    |      | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, *Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices*.

# 6.3 ESD handling ratings

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, use normal handling precautions to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification. During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM), and the charge device model (CDM).

All latch-up testing is in conformity with AEC-Q100 Stress Test Qualification.

A device is defined as a failure if after exposure to ESD pulses, the device no longer meets the device specification. Complete DC parametric and functional testing is performed as per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Characteristic <sup>1</sup>                      | Min   | Мах   | Unit |

|--------------------------------------------------|-------|-------|------|

| ESD for Human Body Model (HBM)                   | -2000 | +2000 | V    |

| ESD for Machine Model (MM)                       | -200  | +200  | V    |

| ESD for Charge Device Model (CDM)                | -500  | +500  | V    |

| Latch-up current at TA= 85°C (I <sub>LAT</sub> ) | -100  | +100  | mA   |

Table 4.

ESD/Latch-up Protection

1. Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

## 6.4 Voltage and current operating ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 5 may affect device reliability or cause permanent damage to the device.

#### NOTE

If the voltage difference between VDD and VDDA or VSS and VSSA is too large, then the device can malfunction or be permanently damaged. The restrictions are:

- At all times, it is recommended that the voltage difference of VDD - VSS be within +/-200 mV of the voltage difference of VDDA - VSSA, including power ramp up and ramp down; see additional requirements in Table 6. Failure to do this recommendation may result in a harmful leakage current through the substrate, between the VDD/VSS and VDDA/VSSA pad cells. This harmful leakage current could prevent the device from operating after power up.

- At all times, to avoid permanent damage to the part, the voltage difference between VDD and VDDA must absolutely be limited to 0.3 V; see Table 5.

- At all times, to avoid permanent damage to the part, the voltage difference between VSS and VSSA must absolutely be limited to 0.3 V; see Table 5.

| Characteristic              | Symbol           | Notes <sup>1</sup> | Min  | Max | Unit |

|-----------------------------|------------------|--------------------|------|-----|------|

| Supply Voltage Range        | V <sub>DD</sub>  |                    | -0.3 | 4.0 | V    |

| Analog Supply Voltage Range | V <sub>DDA</sub> |                    | -0.3 | 4.0 | V    |

Table 5. Absolute Maximum Ratings ( $V_{SS} = 0 V$ ,  $V_{SSA} = 0 V$ )

Table continues on the next page...

| Characteristic                                                                          | Symbol                       | Notes <sup>1</sup> | Min  | Max   | Unit |

|-----------------------------------------------------------------------------------------|------------------------------|--------------------|------|-------|------|

| ADC High Voltage Reference                                                              | V <sub>REFHx</sub>           |                    | -0.3 | 4.0   | V    |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub>                                  | $\Delta V_{DD}$              |                    | -0.3 | 0.3   | V    |

| Voltage difference V <sub>SS</sub> to V <sub>SSA</sub>                                  | $\Delta V_{SS}$              |                    | -0.3 | 0.3   | V    |

| Digital Input Voltage Range                                                             | V <sub>IN</sub>              | Pin Group 1        | -0.3 | 5.5   | V    |

| RESET Input Voltage Range                                                               | V <sub>IN_RESET</sub>        | Pin Group 2        | -0.3 | 4.0   | V    |

| Oscillator Input Voltage Range                                                          | V <sub>OSC</sub>             | Pin Group 4        | -0.4 | 4.0   | V    |

| Analog Input Voltage Range                                                              | V <sub>INA</sub>             | Pin Group 3        | -0.3 | 4.0   | V    |

| Input clamp current, per pin ( $V_{IN} < V_{SS}$ - 0.3 V) <sup>, 2</sup> , <sup>3</sup> | V <sub>IC</sub>              |                    | _    | -5.0  | mA   |

| Output clamp current, per pin <sup>4</sup>                                              | V <sub>oc</sub>              |                    | _    | ±20.0 | mA   |

| Contiguous pin DC injection current—regional limit sum of 16 contiguous pins            | I <sub>ICont</sub>           |                    | -25  | 25    | mA   |

| Output Voltage Range (normal push-pull mode)                                            | V <sub>OUT</sub>             | Pin Group 1, 2     | -0.3 | 4.0   | V    |

| Output Voltage Range (open drain mode)                                                  | V <sub>OUTOD</sub>           | Pin Group 1        | -0.3 | 5.5   | V    |

| RESET Output Voltage Range                                                              | V <sub>OUTOD_RE</sub><br>SET | Pin Group 2        | -0.3 | 4.0   | V    |

| Ambient Temperature                                                                     | T <sub>A</sub>               | V temperature      | -40  | 105   | °C   |

| Junction Temperature                                                                    | Тj                           | V temperature      | -40  | 115   | °C   |

| Storage Temperature Range (Extended Industrial)                                         | T <sub>STG</sub>             |                    | -55  | 150   | °C   |

#### Table 5. Absolute Maximum Ratings ( $V_{SS} = 0 V$ , $V_{SSA} = 0 V$ ) (continued)

#### 1. Default Mode

- Pin Group 1: GPIO, TDI, TDO, TMS, TCK

- Pin Group 2: RESET

- Pin Group 3: ADC and Comparator Analog Inputs

- Pin Group 4: XTAL, EXTAL

- 2. Continuous clamp current

- All 5 volt tolerant digital I/O pins are internally clamped to V<sub>SS</sub> through a ESD protection diode. There is no diode connection to V<sub>DD</sub>. If V<sub>IN</sub> greater than VDIO\_MIN (= V<sub>SS</sub>-0.3 V) is observed, then there is no need to provide current limiting resistors at the pads. If this limit cannot be observed, then a current limiting resistor is required.

- 4. I/O is configured as push-pull mode.

# 7 General

### 7.1 General characteristics

The device is fabricated in high-density, low-power CMOS with 5 V–tolerant TTLcompatible digital inputs, except for the RESET pin which is 3.3V only. The term "5 V– tolerant" refers to the capability of an I/O pin, built on a 3.3 V–compatible process technology, to withstand a voltage up to 5.5 V without damaging the device.

#### General