# Freescale Semiconductor Application Note

AN3379 Rev. 0, 07/2007

# Using the CEA709 eTPU Function

by: Michal Princ System Application Engineer, Roznov Czech System Center

# 1 Introduction

The CEA709 Enhanced Time Processor Unit (eTPU) function serves as a 78.125 kbit/s ANSI/EIA/CEA 709.1 Medium Access Control (MAC) Layer. This function is intended to be used with the ANSI/EIA/CEA 709.1 protocol software developed by Domologic and targeted at Freescale's 32-bit ColdFire controller MCF5235. Then, the MCF5235 can serve as an ASNI/EIA/CEA 709.1 LonTalk® compatible communication node. This application note provides simple C interface routines to the CEA709 eTPU function. These routines are targeted at the MCF523x family of devices, but they could be easily used with any device that has an eTPU.

#### **Contents**

|   | Intro | oduction                       |  |

|---|-------|--------------------------------|--|

| ) | Fun   | ction Overview                 |  |

| 3 | Fun   | Function Description           |  |

|   | 3.1   | RX Channel                     |  |

|   | 3.2   | TX Channel                     |  |

|   | 3.3   | DMA Control Channel 5          |  |

|   | 3.4   | TX Enable Channel 6            |  |

|   | 3.5   | Collision Detection Channel 6  |  |

|   | 3.6   | Noise Immunity                 |  |

|   | 3.7   | Interrupts                     |  |

|   | 3.8   | DMA requests                   |  |

|   | 3.9   | Performance                    |  |

| ŀ | C L   | Level Functions API9           |  |

|   | 4.1   | Initialization Function        |  |

|   | 4.2   | Change Operation Functions     |  |

|   | 4.3   | Value Return Functions         |  |

| 5 | Use   | of Function Example            |  |

|   | 5.1   | Running One CEA709 Instance 16 |  |

|   | 5.2   | Running Two CEA709 Instances   |  |

**Function Overview**

# 2 Function Overview

The CEA709 eTPU function set five functions:

- CEA709 RECEIVE (CEA709\_RX) function uses one input channel to decode differential Manchester encoded signals from a LON® (Local Operating Network) transceiver, check the CRC (Cyclic Redundancy Check) at the end of the received packet, and maintain a receive buffer.

- CEA709 TRANSMIT (CEA709\_TX) function uses one output channel to generate differential Manchester coded signals (packets), calculate and generate the CRC at the end of the transmitted packet, and maintain two transmit buffers.

- CEA709 DMA CONTROL (CEA709\_DMA\_CONTROL) function uses one output channel for generating a DMA transfer trigger signal.

- CEA709 TRANSMIT ENABLE (CEA709\_TXEN) function uses one output channel for transmit enable signal generation. It is an optional channel.

- CEA709 COLLISION DETECTION (CEA709\_CD) function uses one input channel that manages the collision detection signal. It is an optional channel.

# **3 Function Description**

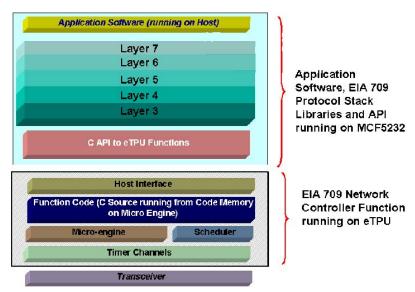

The CEA709 eTPU function, working together with the Domologic protocol stack, serves as an ANSI/EIA/CEA-709 communication node. The CEA709 eTPU function covers layer two of the protocol (see Figure 1), managing the following tasks:

- Receiving physical protocol data unit (PPDU) frames from physical transceiver and their decoding

- Generating and sending PPDU frames to physical transceiver (differential Manchester encoded signal)

- Establishing and maintaining buffers allowing data to be transferred between the CPU and the eTPU/MAC layer

- Generating interrupt requests and DMA requests to manage buffers

- Receiving MAC protocol data unit (MPDU) frames from the CPU and generating PPDU frames for transmission to the transceiver

- Extracting MPDUs from received PPDU data frames and transferring them to the CPU

- Backlog calculation and update

- CRC generation and checking

Figure 1. OSI Reference Model

The CEA709 eTPU function is an equivalent of the Neuron<sup>®</sup> Chip communications port configured to operate in direct mode. The CEA709 eTPU function encodes transmitted data and decodes received data using Differential Manchester coding (also known as bi-phase space coding). This scheme provides a transition at the beginning of every bit period for the purpose of synchronizing the receiver clock. The 0/1 data is indicated by the presence or absence of a second transition halfway between clock transitions. A mid-cell transition indicates a zero. Lack of a mid-cell transition indicates a one. Differential Manchester coding is polarity-insensitive. Therefore, reversal of polarity in the communication link does not affect data reception.

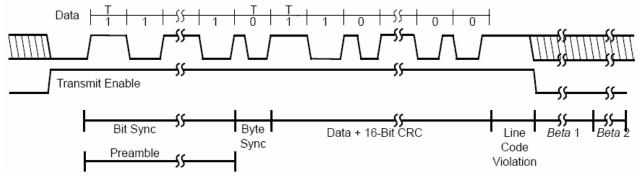

The transmitter transmits a preamble at the beginning of a packet to allow the other nodes to synchronize their receiver clocks. The preamble consists of a series of Differential Manchester ones. Its duration is at least 6 bits long and is selectable. The preamble ends with a single byte-sync bit, which marks the start of byte boundaries on the following bit. The byte-sync bit is a Differential Manchester 0.

The CEA709 eTPU function terminates the packet by forcing a Differential Manchester code violation. After sending the last CRC bit, it holds the data output transitionless for 3 bit periods.

The CEA709 communication bit rate equals 78.125 kbit/s, i.e. one bit period takes 12.8µs. Figure 2 shows a typical packet, where T is the bit period, equal to 1/(bit rate).

Figure 2. CEA709 Protocol Single-Ended Mode Data Format

Using the CEA709 eTPU Function, Rev. 0

Freescale Semiconductor 3

#### **Function Description**

## 3.1 RX Channel

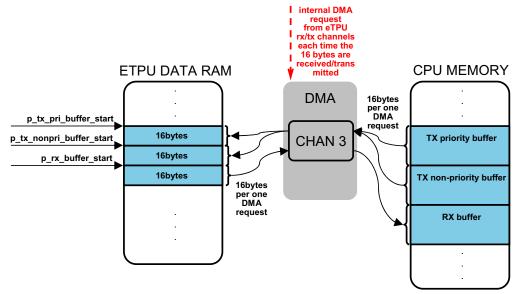

The CEA709 RX channel manages a 16-byte long RX buffer located in the eTPU DATA RAM, see Figure 3. After the RX buffer is full, a DMA transfer is generated to empty the buffer. This transfers newly received data from the eTPU RX buffer to the defined memory place in the CPU. Apart from the DMA request, interrupt requests are generated to the CPU. An interrupt may be requested from the eTPU under the following conditions:

- When a LCV (line code violation = end of frame) has been received to re-initialize the DMA registers (source and destination addresses).

- When an error occurred

- When the backlog value overflows

## 3.2 TX Channel

The CEA709 TX channel manages two TX buffers. It deals with a tx\_priority buffer and a tx\_non-priority buffer, each occupying 16 bytes of the eTPU DATA RAM, see Figure 3. When a frame has to be sent, the CPU copies the first 16 bytes of the message to the eTPU shared memory and then initiates a send request (for non-priority or priority messages) using the defined API function. When the communication media has been granted to the eTPU, the eTPU TX channel requests an interrupt to the CPU. The CPU has to re-configure the DMA channel for sending (normally, the DMA channel used is configured for receiving). Because it is clear now if a priority or non-priority message has to be sent, the CPU sets the DMA source pointer accordingly. The eTPU fetches the data from the CPU memory using DMA requests. When sending, an interrupt may be requested from the eTPU under the following conditions:

- When the transmission begins and the CPU has to configure the DMA controller for sending

- When the message has been transmitted completely

- When an error occurred

- When the backlog value overflows

- When a collision is detected during the preamble or at the end of a packet

The CEA709 eTPU function parameter status reflects the actual status of the eTPU based MAC Layer. This parameter is accessible from the eTPU and the CPU. The CPU can read, set, or clear particular bits using the defined API functions. It deals with the following status data:

```

FS ETPU CEA709 STATUS RX FRAME END

0x000001 // End of frame = line code violation

FS ETPU CEA709 STATUS RX ERROR

0x000002 // Error occurred when receiving

FS ETPU CEA709 STATUS TX PRI BUFFER FULL

0x000004 // TX priority buffer contains

new data to be transmitted

0 \times 0000008 // TX non-priority buffer contains new data to

FS ETPU CEA709 STATUS TX NONPRI BUFFER FULL

be transmitted

FS ETPU CEA709 STATUS TX TRANSMISSION BEGINNING

0x000010 // Transmission begins

FS ETPU CEA709 STATUS TX TRANSMISSION SUCCESSFUL 0x000020 // Data transmitted successfully

FS ETPU CEA709 STATUS TX ERROR

0x000040 // Error occurred when transmitting

FS ETPU CEA709 STATUS BACKLOG OVERFLOW

0x000080 // Backlog overflow

FS ETPU CEA709 STATUS COLLISION DETECTED

0x000100 // Collision detected during the preamble or at

the end of a packet

```

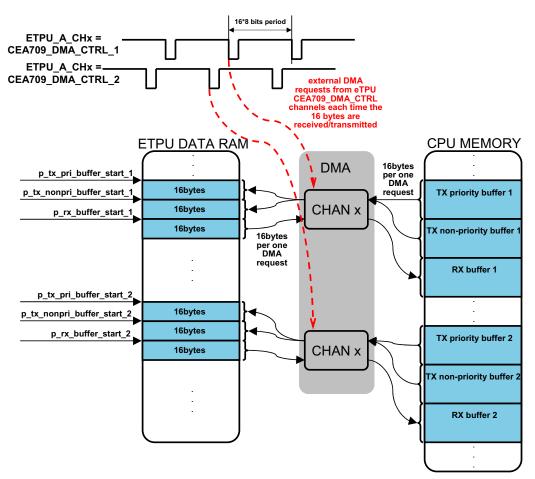

#### 3.3 **DMA Control Channel**

The CEA709 DMA control channel generates the DMA transfer trigger signal. This function is optional and used if the DMA transfers cannot be triggered internally. This can happen when two or more CEA709 instances are running on one eTPU and the DMA module is not able to recognize which of the eTPU channels has asserted the DMA request. To deal with this, the CEA709 DMA CONTROL channel has to be initialized and its output pin has to be connected with the applicable DREQ pin. The DMA triggering signal polarity is selectable, the trigger edge can be low-high or high-low.

Figure 3 and Figure 4 describes the linkage between the eTPU, the DMA, and the CPU. The operation of one eTPU CEA709 instance is described in Figure 3. Figure 4 shows the operation of two eTPU CEA709 instances.

Figure 3. Operation of One eTPU CEA709 Instance – Internal Triggering of the DMA Transfers

#### **Function Description**

Figure 4. Operation of Two eTPU CEA709 Instances – External Triggering of the DMA Transfers

## 3.4 TX Enable Channel

The CEA709 TX enable channel is one of the optional channels. The transmit enable signal on the TX enable channel determines the time the TX channel transmits (see Figure 2). Before beginning to transmit the packet, the transmit enable pin is driven high. At the end of the packet after a Differential Manchester code violation, the transmit enable pin is driven low, indicating the end of transmission. Usage of the TX enable channel depends on the type of transceiver.

## 3.5 Collision Detection Channel

As an option, the CEA709 eTPU MAC unit accepts an active-low Collision Detect (CD) input from the transceiver. If collision detection is enabled and the CD signal goes low for at least one sixty-fourth of a bit period (200 ns) during transmission, the CEA709 eTPU MAC is signalled that a collision has or is occurring. The collision detect flag is checked optionally at the end of the preamble and at the end of the packet. When a collision is detected, the applicable bit in the status parameter is set to one (FS\_ETPU\_CEA709\_STATUS\_COLLISION\_DETECTED), and the CD eTPU channel generates an interrupt to the CPU, indicating that the message must be sent again.

If the node does not use collision detection, the only way it can determine that a message has not been received is to request an acknowledgment.

# 3.6 Noise Immunity

When receiving, the CEA709 function uses an acceptance windows, defined in time, within which the next transition on the RX channel is expected. It deals with the receiver jitter tolerance windows. The window opening and closing times are calculated based on the last window end and the given coefficients (jitter1, jitter2). Two windows are set up for each bit period, T. The first window is set at T/2 and determines if a 0 is being received. The second window is at T and defines a 1 being received. If no transition occurs, a Manchester code violation is detected and the packet is assumed to have ended. If a transition falls outside of either window, it is not detected. Timing instability of the transitions, known as jitter, may be caused by changes in the communications medium or instability in the transmitting or receiving node's input clocks.

Apart from receiver jitter tolerance windows, another noise immunity technique is used on the CEA709 RX channel. When the RX transitions are serviced, it is checked to see whether the input pin has changed since the transition time. If the input pin has changed (a very narrow pulse has occurred), the transition is evaluated as a noise transition and the eTPU waits for a valid transition.

# 3.7 Interrupts

This paragraph summarizes the conditions under which interrupts from the eTPU CEA709 channels are requested:

- RX channel

- A LCV (line code violation = end of frame) has been received

- An error occurred

- The backlog value overflows

- TX channel

- The transmission begins and the CPU has to configure the DMA controller for sending

- The message has been transmitted completely

- An error occurred

- The backlog value overflows

- A collision is detected during the preamble or at the end of the packet

- DMA Control channel does not generate any interrupt

- TX Enable channel does not generate any interrupt

- Collision Detection channel does not generate any interrupt

Apart from these interrupts, the applicable DMA channel has to be configured to generate an interrupt request to the CPU each time a successful DMA transfer finishes (see Figure 3). The interrupt handler then re-configures the DMA channel registers (source and destination addresses, BCR) to be ready for the next DMA transfer. This must be done by the time the next DMA transfer is requested. With regards to 78.125 kbit/s communication, the time between two consecutive DMA transfer requests is 16\*8/(78.125\*1024) = 1.6ms.

Freescale Semiconductor 7

Using the CEA709 eTPU Function, Rev. 0

**Function Description**

# 3.8 DMA requests

As described in previous paragraphs, the DMA requests can be generated internally or externally, depending on the application needs. The CEA709 RX channel generates the DMA transfer itself or through the DMA control channel each time one of eTPU RX channels is full and there is a need to empty the applicable RX buffer. The CEA709 TX channel generates the DMA transfer itself or through the DMA control channel each time the data from the applicable eTPU TX buffer was transmitted and there is a need to fetch new data from the CPU memory. The TX enable channel and the collision detection channel do not generate any DMA requests.

## 3.9 Performance

Like all the eTPU functions, the CEA709 function performance in an application is to some extent dependent upon the service time (latency) of other active eTPU channels. This is due to the operational nature of the scheduler.

The influence of the CEA709 function on the overall eTPU performance can be expressed by the following parameter:

• Maximum eTPU busy-time per one bit period

This value, compared to the bit period value (1/bit rate), determines the proportional load on the eTPU engine caused by the CEA709 function.

Table 1 lists the maximum eTPU busy-times per bit period in eTPU cycles that depend on whether the CEA709 function is transmitting or receiving

| Communication States    | Maximum eTPU busy-time per one bit period [eTPU cycles] |

|-------------------------|---------------------------------------------------------|

| Receiving of packets    | 267                                                     |

| Transmitting of packets | 141                                                     |

**Table 1. Maximum eTPU Busy-times**

The eTPU module clock is equal to the peripheral clock, which is half the CPU clock, on the MCF523x devices. For example, the eTPU module clock is 75 MHz on a 150 MHz MCF5235 and one eTPU cycle takes 13.33ns. Considering a 78.125 kbit/s communication rate, the maximum percentage eTPU load is 267\*100\*78.125/75000 = 27.8% when receiving, and 175\*100\*78.125/75000 = 14.7% when transmitting.

The performance is influenced by compiler efficiency. The above numbers, measured on code compiled by the eTPU compiler version 1.0.7, are given for guidance only and are subject to change. For up to date information, refer to the information provided in the particular eTPU function set release available from Freescale.

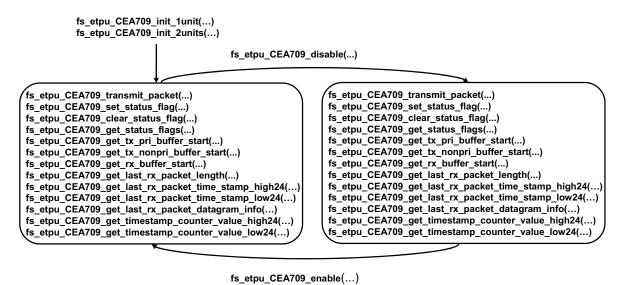

The following routines provide easy access, for the application developer, to the CEA709 function. Use of these functions eliminates the need to directly control the eTPU registers. There are 17 functions added to the application programming interface (API). The routines can be found in the etpu\_CEA709.h and etpu\_CEA709.c files, which should be included in the link file along with the top level development file(s). Figure 5 shows the CEA709 API state flow and lists the API functions that can be used in each of its states.

Figure 5. CEA709 API State Flow

All CEA709 API routines are described in order and listed below:

• Initialization Functions:

```

int32 t fs etpu CEA709 init 1unit( uint8 t

rx channel,

uint8 t

tx_channel,

uint8 t

preamble length,

uint24 t

packet cycle,

uint24 t beta2 control,

uint24 t xmit interpacket,

uint24 t receive interpacket,

uint8_t

channel priorities,

uint8 t

node priority,

uint8 t

bit sync threshold,

uint8 t

dma control channel,

uint8 t

dma trigger mode,

tx en channel,

uint8 t

uint8 t

cd channel,

uint8 t

cd preamble,

uint8 t

cd tail,

uint24 t

cd to end packet)

int32 t fs etpu CEA709 init 2units( uint8 t

rx channel 1,

tx channel_1,

uint8 t

preamble length 1,

uint8 t

uint24 t packet cycle 1,

uint24 t beta2 control 1,

```

Using the CEA709 eTPU Function, Rev. 0

Freescale Semiconductor 9

```

uint24 t xmit interpacket 1,

uint24 t receive interpacket 1,

uint8 t channel priorities 1,

uint8 t node priority 1,

uint8 t

bit sync threshold 1,

uint8 t

dma_control_channel_1,

uint8 t

dma trigger mode 1,

uint8 t

tx en channel 1,

uint8 t

cd channel 1,

uint8 t

cd preamble 1,

uint8 t

cd_tail_1,

uint24_t cd_to_end_packet_1,

uint8 t rx channel 2,

uint8 t tx channel 2,

uint8 t preamble length 2,

uint24 t packet cycle 2,

uint24 t beta2 control 2,

uint24_t xmit_interpacket_2,

uint24 t receive interpacket 2,

uint8 t channel priorities 2,

node_priority_2,

uint8 t

uint8 t

bit_sync_threshold_2,

uint8 t

dma_control_channel_2,

uint8_t

dma_trigger_mode_2,

uint8 t tx en channel 2,

uint8 t

cd channel 2,

uint8 t

cd preamble 2,

uint8 t

cd tail 2,

uint24 t cd to end packet 2)

```

## • Change Operation Functions:

```

uint32 t fs etpu CEA709 enable(uint8 t

rx channel,

uint8 t

tx channel,

uint8 t

dma control channel,

uint8 t

tx en channel,

uint8 t

cd channel)

uint32 t fs etpu CEA709 disable(uint8 t

rx channel,

uint8 t

tx channel,

uint8 t

dma_control_channel,

uint8 t

tx_en_channel,

cd channel)

uint8 t

int32_t fs_etpu_CEA709_transmit_packet(uint8_t rx_channel)

uint32 t fs etpu CEA709 set status flag(uint8 t rx channel, uint32 t mask)

uint32 t fs etpu CEA709 clear status flag(uint8 t rx channel, uint32 t mask)

```

### • Value Return Functions:

```

uint32_t fs_etpu_CEA709_get_tx_pri_buffer_start(uint8_t rx_channel)

uint32_t fs_etpu_CEA709_get_tx_nonpri_buffer_start(uint8_t rx_channel)

uint32_t fs_etpu_CEA709_get_rx_buffer_start(uint8_t rx_channel)

uint24_t fs_etpu_CEA709_get_status_flags(uint8_t rx_channel)

uint24_t fs_etpu_CEA709_get_last_rx_packet_length(uint8_t rx_channel)

uint24_t fs_etpu_CEA709_get_last_rx_packet_time_stamp_high24(uint8_t rx_channel)

uint24_t fs_etpu_CEA709_get_last_rx_packet_time_stamp_low24(uint8_t rx_channel)

uint8_t fs_etpu_CEA709_get_last_rx_packet_datagram_info(uint8_t rx_channel)

uint24_t fs_etpu_CEA709_get_timestamp_counter_value_high24(uint8_t rx_channel)

uint24_t fs_etpu_CEA709_get_timestamp_counter_value_low24(uint8_t rx_channel)

```

Using the CEA709 eTPU Function, Rev. 0

10 Freescale Semiconductor

## 4.1 Initialization Function

## 4.1.1 Initialize One MAC Unit

The int32\_t fs\_etpu\_CEA709\_init\_1unit routine initializes one CEA709 MAC unit. This function has the following parameters:

- rx channel (uint8 t) RX channel number (CP0)

- tx channel (uint8 t) TX channel number (CP1)

- preamble length (uint8 t) length of preamble for direct mode (in number of bits)

- packet cycle (uint24 t) packet cycle duration (in number of bits)

- beta2 control (UINT24 T) beta2 slots width (in number of bits)

- xmit interpacket (uint24 t) interpacket padding after transmitting (in number of bits)

- receive interpacket (uint24 t) interpacket padding after receiving (in number of bits)

- channel priorities (uint8 t) number of priority slots on the channel

- node\_priority (uint8\_t) priority slot used by the node when sending priority messages on the channel (1 255). It should not be greater than the number of priority slots on the channel. If the node has no priority slot allocated, this is 0.

- bit sync threshold (uint8 t) number of sync bits

- dma\_control\_channel (uint8\_t) DMA control channel number necessary for external DMA request generation

- dma\_trigger\_mode (uint8\_t) this parameter defines the polarity on DMA CONTROL channel and it should be assigned a value of:

```

FS_ETPU_CEA709_DMA_TRIGGER_RISING_EDGE or FS_ETPU_CEA709_DMA_TRIGGER_FALLING_EDGE or FS_ETPU_CEA709_DMA_TRIGGER_INTERNAL.

```

- tx\_en\_channel (uint8\_t) transmit enable channel number (CP2,if required); If not applicable then set to FS\_ETPU\_CEA709\_CHAN\_NOT\_USED.

- cd\_channel (uint8\_t) collision detection channel number (CP4,if required); If not applicable then set to FS\_ETPU\_CEA709\_CHAN\_NOT\_USED.

- cd\_preamble (uint8\_t) this parameter determines whether the CD signal is checked at the end of the packet preamble; this parameter should be assigned a value of:

```

FS_ETPU_CEA709_CDPREAMBLE_NO or FS_ETPU_CEA709_CDPREAMBLE_YES

```

• cd\_tail (uint8\_t) – this parameter determines whether the CD signal is checked at the end of the packet; this parameter should be assigned a value of:

```

FS_ETPU_CEA709_CDTAIL_NO or FS_ETPU_CEA709_CDTAIL_YES

```

• cd\_to\_end\_packet (uint24\_t) – how close to the end of the packet the CD signal is checked (in number of bits)

## 4.1.2 Initialize Two MAC Units

The int32\_t fs\_etpu\_CEA709\_init\_2units routine initializes two CEA709 MAC units. This function has the following parameters:

- rx channel 1 (uint8 t) RX channel number (CP0) of unit 1

- tx channel 1 (uint8 t) TX channel number (CP1) of unit 1

- preamble\_length\_1 (uint8\_t) length of preamble for direct mode (in number of bits) of unit 1

- packet cycle 1 (uint24 t) packet cycle duration (in number of bits) of unit 1

- beta2\_control\_1 (uint24\_t) beta2 slots width (in number of bits) of unit 1

- xmit\_interpacket\_1 (uint24\_t) interpacket padding after transmitting (in number of bits) on unit 1

- receive interpacket 1 (uint24 t) interpacket padding after receiving (in number of bits) on unit 1

- channel priorities 1 (uint8 t) number of priority slots on the channel of unit 1

- node\_priority\_1 (uint8\_t) unit 1 priority slot used by the node when sending priority messages on the channel (1 255). It should not be greater than the number of priority slots on the channel. If the node has no priority slot allocated, this is 0

- bit sync threshold 1 (uint8 t) number of sync bits of unit 1

- dma\_control\_channel\_1 (uint8\_t) DMA control channel number necessary for external DMA request generation for unit 1

- dma\_trigger\_mode\_1 (uint8\_t) This parameter defines the polarity on the DMA CONTROL channel of unit 1. This parameter should be assigned a value of:

FS ETPU CEA709 DMA TRIGGER RISING EDGE or

```

FS_ETPU_CEA709_DMA_TRIGGER_RISING_EDGE or FS_ETPU_CEA709_DMA_TRIGGER_FALLING_EDGE or FS_ETPU_CEA709_DMA_TRIGGER_INTERNAL.

```

- tx\_en\_channel\_1 (uint8\_t) transmit enable channel number (CP2,if required) of unit 1; If not applicable then set to FS\_ETPU\_CEA709\_CHAN\_NOT\_USED.

- cd\_channel\_1 (uint8\_t) collision detection channel number (CP4,if required) of unit 1; If not applicable then set to FS\_ETPU\_CEA709\_CHAN\_NOT\_USED.

- cd\_preamble\_1 (uint8\_t) this parameter determines whether the CD signal is checked at the end of the packet preamble; this parameter should be assigned a value of:

```

FS_ETPU_CEA709_CDPREAMBLE_NO or FS_ETPU_CEA709_CDPREAMBLE_YES

```

• cd\_tail\_1 (uint8\_t) – this parameter determines whether the CD signal is checked at the end of the packet; this parameter should be assigned a value of:

```

FS_ETPU_CEA709_CDTAIL_NO or FS_ETPU_CEA709_CDTAIL_YES

```

- cd\_to\_end\_packet\_1 (uint24\_t) how close to the end of the packet the CD signal is checked (in number of bits)

- rx\_channel\_2 (uint8\_t) RX channel number (CP0) of unit 2

- tx\_channel\_2 (uint8\_t) TX channel number (CP1) of unit 2

- preamble\_length\_2 (uint8\_t) length of preamble for direct mode (in number of bits) of unit 2

- packet\_cycle\_2 (uint24\_t) packet cycle duration (in number of bits) of unit 2

- beta2 control 2 (uint24 t) beta2 slots width (in number of bits) of unit 2

- xmit interpacket 2 (uint24 t) interpacket padding after transmitting (in number of bits) on unit 2

- receive interpacket 2 (uint24 t) interpacket padding after receiving (in number of bits) on unit 2

- channel priorities 2 (uint8 t) number of priority slots on the channel of unit 2

- node\_priority\_2 (uint8\_t) unit 2 priority slot used by the node when sending priority messages on the channel (1 255). It should not be greater than the number of priority slots on the channel. If the node has no priority slot allocated, this is 0.

- bit sync threshold 2 (uint8 t) number of sync bits of unit 2

- dma\_control\_channel\_2 (uint8\_t) DMA control channel number necessary for external DMA request generation for unit 2

- dma\_trigger\_mode\_2 (uint8\_t) This parameter defines the polarity on the DMA CONTROL channel of unit 2. This parameter should be assigned a value of:

FS\_ETPU\_CEA709\_DMA\_TRIGGER\_RISING\_EDGE or

FS\_ETPU\_CEA709\_DMA\_TRIGGER\_FALLING\_EDGE or

FS\_ETPU\_CEA709\_DMA\_TRIGGER\_INTERNAL.

- tx\_en\_channel\_2 (uint8\_t) transmit enable channel number (CP2, if required) of unit 2; If not applicable, set to FS\_ETPU\_CEA709\_CHAN\_NOT\_USED.

- cd\_channel\_2 (uint8\_t) collision detection channel number (CP4, if required) of unit 2; If not applicable, set to FS\_ETPU\_CEA709\_CHAN\_NOT\_USED.

- cd\_preamble\_2 (uint8\_t) this parameter determines whether the CD signal is checked at the end

of the packet preamble; this parameter should be assigned a value of:

FS\_ETPU\_CEA709\_CDPREAMBLE\_NO or

FS\_ETPU\_CEA709\_CDPREAMBLE\_YES

- cd\_tail\_2 (uint8\_t) this parameter determines whether the CD signal is checked at the end of the packet; this parameter should be assigned a value of:

FS\_ETPU\_CEA709\_CDTAIL\_NO or

FS\_ETPU\_CEA709\_CDTAIL\_YES

- cd\_to\_end\_packet\_2 (uint24\_t) how close to the end of the packet the cd signal is checked (in number of bits)

# 4.2 Change Operation Functions

The uint32\_t fs\_etpu\_CEA709\_enable function enables the CEA709 eTPU channels. This function has the following parameters:

- rx channel (uint8 t) RX channel number (CP0)

- tx channel (uint8 t) TX channel number (CP1)

- dma\_control\_channel (uint8\_t) DMA control channel number necessary for external DMA request generation

- tx en channel (uint8 t) transmit enable channel number (CP2, if required)

- cd channel (uint8 t) collision detection channel number (CP4, if required)

The uint32\_t fs\_etpu\_CEA709\_disable function disables the CEA709 eTPU channels. This function has the following parameters:

- rx channel (uint8 t) RX channel number (CP0)

- tx channel (uint8 t) TX channel number (CP1)

- dma\_control\_channel (uint8\_t) DMA control channel number necessary for external DMA request generation

- tx\_en\_channel (uint8\_t) transmit enable channel number (CP2, if required)

- cd\_channel (uint8\_t) collision detection channel number (CP4, if required)

The CPU requests transmission of the next packet by calling the int32\_t fs\_etpu\_CEA709\_transmit\_packet. Each time the CPU has new data to transmit, it writes the data to the applicable TX buffer, sets the applicable status flags, and calls this function. This function has the following parameter:

• rx channel (uint8 t) – RX channel number (CP0)

The uint32\_t fs\_etpu\_CEA709\_set\_status\_flag function sets the appropriate status flag. This function has the following parameters:

- rx channel (uint8 t) RX channel number (CP0)

- mask (uint32\_t) determines which status flag should be set. This parameter should be assigned a value of:

```

FS ETPU CEA709 STATUS RX FRAME END

0x000001 // End of frame equals line code

violation

FS ETPU CEA709 STATUS RX ERROR

0x000002 // Error occurred when receiving

FS ETPU CEA709 STATUS TX PRI BUFFER FULL

0x000004 // TX priority buffer contains new

data to be transmitted

FS ETPU CEA709 STATUS TX NONPRI BUFFER FULL

0x000008 // TX non-priority buffer contains new

data to be transmitted

FS ETPU CEA709 STATUS TX TRANSMISSION BEGINNING 0x000010 // Transmission begins

FS ETPU CEA709 STATUS TX TRANSMISSION SUCCESSFUL 0x000020 // Data transmitted successfully

FS ETPU CEA709 STATUS TX ERROR

0x000040 // Error occurred when transmitting

FS ETPU CEA709 STATUS BACKLOG OVERFLOW

0x000080 // Backlog overflow

FS_ETPU_CEA709_STATUS_COLLISION_DETECTED

0 \times 000100 // Collision detected during the

preamble or at the end of the packet

```

The uint32\_t fs\_etpu\_CEA709\_clear\_status\_flag function enables the clearing of the appropriate status flag. This function has the following parameters:

- rx channel (uint8 t) RX channel number (CP0)

- mask (uint32\_t) determines which status flag should be cleared. This parameter should be assigned a value of:

```

FS ETPU CEA709 STATUS RX_FRAME_END

0x000001 // End of frame equals line code

violation

FS ETPU CEA709 STATUS RX ERROR

0x000002 // Error occurred when receiving

FS_ETPU_CEA709_STATUS_TX_PRI_BUFFER_FULL

0x000004 // TX priority buffer contains new

data to be transmitted

FS ETPU CEA709 STATUS TX NONPRI_BUFFER_FULL

0x000008 // TX non-priority buffer contains new

data to be transmitted

0 \times 000010 // Transmission begins

FS ETPU CEA709 STATUS TX TRANSMISSION BEGINNING

FS_ETPU_CEA709_STATUS_TX_TRANSMISSION_SUCCESSFUL_0x000020_// Data transmitted successfully

FS_ETPU_CEA709_STATUS_TX_ERROR

0 \times 000040 // Error occurred when transmitting

0x000080 // Backlog overflow

FS ETPU CEA709 STATUS BACKLOG OVERFLOW

FS ETPU CEA709 STATUS COLLISION DETECTED

0x000100 // Collision detected during the

preamble or at the end of the packet

```

## 4.3 Value Return Functions

The uint32\_t fs\_etpu\_CEA709\_get\_tx\_pri\_buffer\_start function gets the pointer to the beginning of the transmit priority buffer. This function has the following parameter:

• rx channel (uint8 t) – RX channel number (CP0)

The pointer to the beginning of the transmit priority buffer is returned as an uint32 t.

The uint32\_t fs\_etpu\_CEA709\_get\_tx\_nonpri\_buffer\_start function gets the pointer to the beginning of the transmit non-priority buffer. This function has the following parameter:

• rx\_channel (uint8\_t) – RX channel number (CP0)

The pointer to the beginning of the transmit non-priority buffer is returned as an uint32\_t.

This uint32\_t fs\_etpu\_CEA709\_get\_rx\_buffer\_start function gets the pointer to the beginning of the receive buffer. This function has the following parameter:

• rx\_channel (uint8\_t) – RX channel number (CP0)

The pointer to the beginning of the receive buffer is returned as an uint32 t.

This uint24\_t fs\_etpu\_CEA709\_get\_status\_flags function gets the actual MAC/Link layer status flags for the callback function. This function has the following parameter:

• rx\_channel (uint8\_t) – RX channel number (CP0)

The actual MAC/Link layer status flags are returned as an uint24 t.

This uint24\_t fs\_etpu\_CEA709\_get\_last\_rx\_packet\_length function gets the length of the last received packet. This function has the following parameter:

• RX CHANNEL (UINT8 T) – RX channel number (CP0)

The length of the last received packet is returned as an uint24\_t.

#### **Use of Function Example**

This uint24\_t fs\_etpu\_CEA709\_get\_last\_rx\_packet\_time\_stamp\_high24 function gets the upper 24 bits of the last received packet timestamp. This function has the following parameter:

• rx channel (uint8 t) – RX channel number (CP0)

The length of the last received packet is returned as an uint24 t.

This uint24\_t fs\_etpu\_CEA709\_get\_last\_rx\_packet\_time\_stamp\_low24 function gets the lower 24 bits of the last received packet timestamp. This function has the following parameter:

• rx channel (uint8 t) – RX channel number (CP0)

The length of the last received packet is returned as an uint24\_t.

This uint8\_t fs\_etpu\_CEA709\_get\_last\_rx\_packet\_datagram\_info function gets the additional datagram info of the last received packet. This function has the following parameter:

• rx channel (uint8 t) – RX channel number (CP0)

The length of the last received packet is returned as an uint8 t.

This uint24\_t fs\_etpu\_CEA709\_get\_timestamp\_counter\_value\_high24 function gets the upper 24 bits of the timestamp counter value. This function has the following parameter:

• rx\_channel (uint8\_t) – RX channel number (CP0)

The length of the last received packet is returned as an uint24 t.

This uint24\_t fs\_etpu\_CEA709\_get\_timestamp\_counter\_value\_low24 function gets the lower 24 bits of the timestamp counter value. This function has the following parameter:

• rx\_channel (uint8\_t) – RX channel number (CP0)

The length of the last received packet is returned as an uint24\_t.

# 5 Use of Function Example

# 5.1 Running One CEA709 Instance

The following pieces of code serve as examples of using the CEA709 eTPU function API. The CEA709\_DMA\_CONTROL channel is initialized but the DMA triggering is performed internally. When using Echelon FTT-10A free topology twisted pair transceiver, the CEA709\_TXEN and CEA709\_CD channels do not have to be initialized (FTT-10A does not support these functions). The initialization of the CEA709 eTPU function should be as follows:

```

/* initialize one CEA709 function */

err_code = fs_etpu_CEA709_init_lunit(

CEA709_RX_CHAN, /* eTPU channel 0 */

CEA709_TX_CHAN, /* eTPU channel 1*/

23, /* preamble_length */

322, /* packet_cycle */

13, /* beta2_control */

70, /* xmit_interpacket */

72, /* receive_interpacket */

2, /* channel_priorities */

2, /* node_priority */

```

Using the CEA709 eTPU Function, Rev. 0

```

4, /* bit_sync_threshold */

CEA709_DMA_CONTROL_CHAN, /* dma_control_channel */

FS_ETPU_CEA709_DMA_TRIGGER_INTERNAL, /* dma_trigger_mode */

FS_ETPU_CEA709_CHAN_NOT_USED, /* tx_en_channel */

FS_ETPU_CEA709_CHAN_NOT_USED, /* cd_channel */

FS_ETPU_CEA709_CDPREAMBLE_NO, /* cd_preamble */

FS_ETPU_CEA709_CDTAIL_NO, /* cd_tail */

0); /* cd_to_end_packet */

```

It is necessary to enable packet reception/transmission by calling the fs\_etpu\_CEA709\_enable() function after the CEA709 function initialization. When the CEA709 channels have been disabled, use the same function to restart.

To obtain addresses of the eTPU RX and TX buffers, call the following functions. This is essential for further DMA channel configuration settings.

```

/* read addresses of the eTPU RX/TX buffers */

CEA709_rx_buffer_start_addr =

fs_etpu_CEA709_get_rx_buffer_start(CEA709_RX_CHAN);

CEA709_tx_pri_buffer_start_addr =

fs_etpu_CEA709_get_tx_pri_buffer_start(CEA709_RX_CHAN);

CEA709_tx_nonpri_buffer_start_addr =

fs_etpu_CEA709_get_tx_nonpri_buffer_start(CEA709_RX_CHAN);

```

To transmit a new packet through the eTPU CEA709 function, the following actions have to be done. Fill the CPU priority/non-priority buffer by the MPDU and copy the first 16 bytes from the CPU priority/non-priority buffer to the applicable eTPU TX buffers. Then set the applicable status flags and call the fs etpu CEA709 transmit packet() function as follows:

**Use of Function Example**

# 5.2 Running Two CEA709 Instances

The following piece of code demonstrates how to configure the eTPU for two CEA709 instances. As the DMA module on MCF523x is not able to recognize which of the eTPU channels asserted the DMA request, it is necessary to trigger the DMA transfer using an external DMA request. The CEA709\_DMA\_CONTROL channel has to be initialized and its output pin has to be connected with the applicable DREQ pin. The initialization of the CEA709 eTPU functions should be as follows:

```

/* initialize the first CEA709 instance */

err code = fs etpu CEA709 init 2units(

CEA7091 RX CHAN, /* eTPU channel 0 */

CEA7091_TX_CHAN, /* eTPU channel 1 */

23, /* preamble length */

322, /* packet cycle */

13, /* beta2_control */

70, /* xmit_interpacket */

72, /* receive interpacket */

2, /* channel priorities */

2, /* node priority */

4, /* bit sync threshold */

CEA7091 DMA CONTROL CHAN, /* dma control channel (2) */

FS ETPU CEA709 DMA TRIGGER FALLING EDGE, /* dma trigger mode */

CEA7091 TXEN CHAN, /* tx en channel (3) */

CEA7091_CD_CHAN, /* cd channel (4) */

FS ETPU_CEA709_CDPREAMBLE_YES, /* cd_preamble */

FS ETPU CEA709 CDTAIL YES, /* cd tail */

10, /* cd to end packet */

CEA7092 RX CHAN, /* eTPU channel 5 */

CEA7092 TX CHAN, /* eTPU channel 6 */

23, /* preamble length */

322, /* packet_cycle */

13, /* beta2 control */

70, /* xmit_interpacket */

72, /* receive interpacket */

2, /* channel priorities */

2, /* node priority */

4, /* bit_sync_threshold */

CEA7092 DMA CONTROL CHAN, /* dma control channel (7) */

FS_ETPU_CEA709_DMA_TRIGGER_FALLING_EDGE, /* dma trigger mode */

CEA7092 TXEN CHAN, /* tx en channel (8) */

CEA7092 CD CHAN, /* cd channel (9) */

FS ETPU CEA709 CDPREAMBLE YES, /* cd preamble */

FS ETPU CEA709 CDTAIL YES, /* cd tail */

10); /* cd to end packet */

```

Determine which CEA709 instance the called API function refers to each time the API functions are used. This is done by assigning to the rx\_channel parameter of the API functions the applicable CEA709 instance RX channel number.

## THIS PAGE IS INTENTIONALLY BLANK

#### How to Reach Us:

**Home Page:**

www.freescale.com

Web Support:

http://www.freescale.com/support

**USA/Europe or Locations Not Listed:** Freescale Semiconductor, Inc.

Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French)

Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

www.freescale.com/support

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Inďustrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: AN3379 Rev. 0 07/2007

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007. All rights reserved.